VIA Nano - VIA Nano

| |

| Allmän information | |

|---|---|

| Marknadsförs av | VIA Technologies |

| Designad av | Centaur Technology |

| Gemensamma tillverkare | |

| Prestanda | |

| FSB -hastigheter | 533 MHz till 1066 MHz |

| Cache | |

| L1 -cache | 64 KiB -instruktion + 64 KiB -data per kärna |

| L2 -cache | 1 MiB per kärna |

| Arkitektur och klassificering | |

| Min. funktioner storlek | 40 nm till 65 nm |

| Mikroarkitektur | VIA Jesaja |

| Instruktionsuppsättning | x86-64 |

| Fysiska specifikationer | |

| Kärnor | |

| Paket (er) | |

| Produkter, modeller, varianter | |

| Kärnnamn | |

| Historia | |

| Företrädare | VIA C7 |

Den VIA Nano (tidigare kodnamnet VIA Isaiah ) är en 64-bitars CPU för persondatorer . Den VIA Nano släpptes av VIA Technologies 2008 efter fem år av utveckling av dess CPU division, Centaur Technology . Denna nya Isaiah 64-bitars arkitektur designades från grunden, presenterades den 24 januari 2008 och lanserades den 29 maj, inklusive lågspänningsvarianter och varumärket Nano. Processorn stöder ett antal VIA-specifika x86- tillägg som är utformade för att öka effektiviteten i lågeffektapparater.

Historia

Till skillnad från Intel och AMD använder VIA två distinkta utvecklingskodnamn för var och en av sina CPU -kärnor. I det här fallet användes kodnamnet 'CN' i USA av Centaur Technology. Bibliska namn används som koder av VIA i Taiwan , och Jesaja var valet för just denna processor och arkitektur. Det förväntas att VIA Isaiah kommer att vara dubbelt så snabbt i heltalsprestanda och fyra gånger så snabbt i flytande prestanda som föregående generationens VIA Esther med en motsvarande klockfart . Strömförbrukningen förväntas också vara i nivå med tidigare generationens VIA-processorer, med termisk designeffekt som sträcker sig från 5 W till 25 W. Som en helt ny design byggdes Isaiah-arkitekturen med stöd för funktioner som x86-64- instruktionen set och x86 -virtualisering som inte var tillgängliga på sina föregångare, VIA C7 -linjen, samtidigt som de behåller sina krypteringstillägg. Flera oberoende tester visade att VIA Nano presterar bättre än Intel Atom med en kärna i olika arbetsbelastningar. I ett Ars Technica -test 2008 fick en VIA Nano betydande prestanda i minnesundersystemet efter att dess CPUID ändrades till Intel, vilket antydde möjligheten att benchmark -programvaran bara kontrollerar CPUID istället för de faktiska funktioner som stöds av CPU: n för att välja en kodväg. Referensprogramvaran som användes hade släppts innan VIA Nano släpptes.

Den 3 november 2009 lanserade VIA Nano 3000 -serien. VIA hävdar att dessa modeller kan erbjuda 20% prestandahöjning och 20% mer energieffektivitet än Nano 1000- och 2000 -serien. Benchmarks som drivs av VIA hävdar att en 1,6 GHz 3000-serie Nano kan överträffa den åldrande Intel Atom N270 med cirka 40–54%. 3000 -serien lägger till tillägget SSE4 SIMD -instruktionsuppsättningar, som först introducerades med 45 nm revisioner av Intel Core 2 -arkitekturen.

Den 11 november 2011 släppte VIA VIA Nano X2 Dual-Core Processor med sitt första dubbelkärniga pico-itx-moderkort någonsin. VIA Nano X2 är byggd på en 40 nm process och stöder SSE4 SIMD instruktionsuppsättningar, avgörande för moderna flytpunktsberoende applikationer. Via hävdar 30% högre prestanda jämfört med Intels Atom med en 50% högre klocka.

De Zhaoxin joint venture-processorer, som släpptes från 2014, är baserade på VIA Nano-serien.

Funktioner

- x86-64 instruktionsuppsättning

- Klockhastighet från 1 GHz till 2 GHz

- Busshastighet på 533 MHz eller 800 MHz (1066 MHz för Nano x2)

- 64 KB data och 64 KB instruktioner L1 -cache och 1 MB L2 -cache per kärna.

- 65 nm tillverkningsprocess (40 nm för Nano x2)

- Superscalar utförande av instruktioner som inte är i ordning

- Stöd för MMX, SSE, SSE2, SSE3, SSSE3 och SSE4 instruktionsuppsättning

- Stöd för virtualisering x86 med Intel-kompatibel implementering (inaktiverad innan steg 3)

- Stöd för ECC -minne

- Stiftkompatibel med VIA C7 och VIA Eden

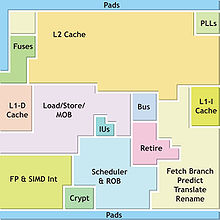

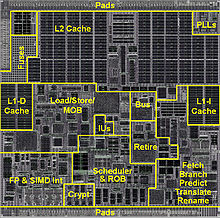

Arkitekturöversikt

- Out-of-order och superscalar design : Ger mycket bättre prestanda än sin föregångare, VIA C7-processorn, som var i ordning. Detta sätter Isaiah -arkitekturen i linje med samma års erbjudanden från AMD och Intel.

- Instruktioner fusion : Tillåter processorn att kombinera några instruktioner som en enda instruktion, minska energikraven och ge högre prestanda (Atom använder en liknande strategi för att behandla x86-instruktioner på ett mer `` helt '' sätt, snarare än att bryta dem i RISC-liknande mikro -ops).

- Förbättrad grenprediktion : Använder åtta prediktorer i två pipelinesteg.

- CPU cache utformning : En exklusiv cache designen gör att innehållet i L1 cache inte dupliceras i L2-cache, vilket ger en större total cache.

-

Dataförhämtning : Innehåller nya mekanismer för dataförhämtning, inklusive både laddning av en särskild 64-raders cache innan L2-cacheminnet laddas och en direkt laddning till L1-cachen.

- Hämtar 4 x86 instruktioner per cykel i motsats till Intels 3-5

- Utfärdar 3 mikrooperationer /klocka till exekveringsenheter

- Minnes tillgång : Sammanslagning av mindre butiker till större lastdata.

-

Exekveringsenheter : Sju exekveringsenheter är tillgängliga, vilket gör att upp till sju mikrooperationer kan utföras per klocka.

- 2 heltalsenheter (ALU1 och ALU2)

- ALU1 är komplett, medan ALU2 saknar några instruktioner för låg användning och därför är mer lämpad för uppgifter som adressberäkningar.

- 2 lagringsenheter, en för adresslager och en för datalagring enligt VIA .

- 1 Lastenhet

- 2 medieenheter (MEDIA-A och MEDIA-B) med en 128-bitars bred datapass , som stöder 4 enkla precisioner eller 2 dubbelprecisionsoperationer. Mediaberäkning avser användningen av de två medieenheterna.

- MEDIA-A utför "add" -instruktioner med flytande punkt (2-klockars latens för enkelprecision och dubbelprecision ), heltal SIMD, kryptering, dividera och kvadratrot.

- MEDIA-B utför "multiplicera" instruktioner med flytande punkter (2-klockars latens för enkel precision, 3-klockers latens för dubbel precision).

- På grund av parallelliteten som introduceras med de 2 medieenheterna kan mediaberäkningen tillhandahålla fyra "lägg till" och fyra "multiplicera" instruktioner per klocka.

- En ny implementering av FP-tillägg med den lägsta klock-latensen för en x86-processor hittills.

- Nästan alla heltal -SIMD -instruktioner körs på en klocka.

- Implementerar MMX , SSE , SSE2 , SSE3 , SSSE3 multimediainstruktioner

- Implementerar SSE4.1 multimedia instruktionsset (VIA Nano 3000 -serien)

- Implementerar SSE4.1 multimedia instruktionsset (VIA Nano x2 -serien)

- 2 heltalsenheter (ALU1 och ALU2)

-

Strömhantering : Förutom att den kräver mycket låg effekt ingår många nya funktioner.

- Inkluderar ett nytt C6 -effektläge (cacher spolas, internt tillstånd sparas och kärnspänning stängs av).

- Adaptiv P-tillståndskontroll : Övergång mellan prestanda och spänningstillstånd utan att stoppa körningen.

- Adaptiv överklockning : Automatisk överklockning om det är låg temperatur i processorkärnan.

- Adaptiv termisk gräns : Justering av processorn för att bibehålla en användares fördefinierade temperatur.

-

Kryptering : Inkluderar VIA PadLock -motorn

- Hårdvarustöd för AES- kryptering, säker hash-algoritm SHA-1 och SHA-256 och slumpmässig nummergenerering

Runt 2014/8/31 ryktades rykten om en potentiell uppdatering av Jesaja II.

Se även

Referenser

externa länkar

Tryck

- "Slaget om lågeffektsprocessorer: Bästa valet för en nätop" . 2008-09-27. Arkiverad från originalet 2013-10-25.

- "Low-end agg-match: Nano vs. Atom" . 2008-07-30.

- "Via Nano L2100 tar sig an Intels Atom 230" . 2008-07-30.