Intel 4004 - Intel 4004

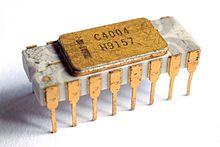

Vit keramik Intel C4004 mikroprocessor med grå spår

| |

| Allmän information | |

|---|---|

| Lanserad | 15 november 1971 |

| Avbruten | 1981 |

| Gemensamma tillverkare | |

| Prestanda | |

| Max. CPU -klockfrekvens | 740-750 kHz |

| Databredd | 4 bitar |

| Adressbredd | 12 bitar (multiplexerade) |

| Arkitektur och klassificering | |

| Ansökan | Busicom -kalkylator, aritmetisk manipulation |

| Min. funktioner storlek | 10 μm |

| Instruktionsuppsättning | 4-bitars BCD- orienterad |

| Fysiska specifikationer | |

| Transistorer | |

| Paket (er) | |

| Uttag | |

| Historia | |

| Efterträdare | Intel 4040 |

Den Intel 4004 är en 4-bitars centralenhet (CPU) släpptes av Intel Corporation 1971. Det var den första kommersiellt producerade mikroprocessor , och den första i en lång rad av Intel-processorer .

Chipdesignen, implementerad med MOS -kiselportstekniken, startade i april 1970 och skapades av Federico Faggin som ledde projektet från början till slut 1971. Marcian Hoff formulerade och ledde arkitektförslaget 1969 och Masatoshi Shima bidrog till arkitekturen och senare till den logiska designen. Den första leveransen av en fullt fungerande 4004 inträffade i mars 1971 till Busicom Corp. i Japan för sin 141-PF utskriftskalkylator-prototyp (nu visas i Computer History Museum i Mountain View, Kalifornien). Denna räknare för vilken 4004 ursprungligen designades och byggdes som ett anpassat chip var först kommersiellt tillgängligt i juli 1971.

Federico Faggin åstadkom det som ingen hade uppnått tidigare: att passa in en CPU för allmänna ändamål i ett litet, kommersiellt kiselchip. Han uppfann hur man designar och layoutar 2300 slumpmässiga logiska transistorer till ett enda chip med 5 gånger hastigheten och två gånger kretstätheten (halva kostnaden) för den nuvarande metallgrindtekniken. Denna oöverträffade integration uppnåddes genom den nya procesteknik han uppfann vid Fairchild Semiconductors 1968, MOS silicon gate technology (SGT), med vilken han också designade den första kommersiella IC (Fairchild 3708). För att utforma Intel 4004 använde Faggin SGT med två nya uppfinningar av honom, den "begravda kontakten" och "bootstrap-belastningen i kiselgrind", vilket möjliggjorde nödvändig hastighet, kraft och kostnad för en användbar allmänprocessor .

4004 var den första slumpmässiga logikkretsen integrerad i ett chip med hjälp av MOS (metall -oxid -halvledare) kiselportsteknik (SGT). Det var den mest avancerade integrerade kretsdesignen (IC) som genomförts fram till dess. Hoff, chef för Intels applikationsforskningsavdelning, hade formulerat ett arkitektoniskt förslag bestående av en blockarkitektur med en instruktionsuppsättning under 1969, medan han pratade med Busicom -ingenjörer under ledning av Shima och med hjälp av Stan Mazor. Hoff och Mazor var inte MOS -chipdesigners och deltog inte i själva designen eller utvecklingen av 4004.

Chipdesignen realiserades oberoende i MOS -avdelningen, annorlunda än Application Research. Det kunde bara förverkligas av en designer med djup kunskap om MOS -processteknik och om den nya SGT. Faggin anställdes på Intel i april 1970 från Fairchild Semiconductor för att vara projektledare och designer för 4004 och han övergick till tillverkning av ett fullt fungerande chip i mars 1971. Faggin förde Intel med sitt behärskning av SGT som han hade uppfunnit på Fairchild ( 1968) och använde den för att utveckla sin nya metod för slumpmässig chipdesign som var nyckeln till att göra de första och alla tidiga Intel -mikroprocessorerna. Shima, som representerar Busicom, var förlovad med Hoff och Mazor under arkitekturen under 1969 och han hjälpte också Faggin med den slutliga logikkonstruktionen i 6 månader 1970.

I november 1971, med den profetiska annonsen "Meddelande om en ny era inom integrerad elektronik", gjordes 4004 kommersiellt tillgänglig för den allmänna marknaden. 4004 var den första monolitiska processorn, helt integrerad i ett litet chip. En sådan integrationsbedrift möjliggjordes av användningen av den nya kiselportstekniken för integrerade kretsar, som ursprungligen utvecklades av Faggin (med Tom Klein) på Fairchild Semiconductor 1968, vilket möjliggjorde två gånger antalet slumpmässiga logiska transistorer och en ökning av hastighet med en faktor fem jämfört med den nuvarande MOS aluminiumgrindtekniken. Faggin uppfann också bagagerumslasten med kiselport och "begravd kontakt", vilket förbättrade hastigheten och kretstätheten jämfört med aluminiumporten.

4004 mikroprocessorn, 4001 ROM, 4002 RAM och 4003 skiftregister utgjorde de fyra chipsen i Intel MCS-4 chipset. Med dessa komponenter kunde små datorer med varierande mängder minne och I/O -anläggningar byggas.

Samtidiga CPU -chips

Tre andra CPU-chipdesigner togs fram ungefär samtidigt: Four-Phase Systems AL1, gjord 1969; den MP944 , som blev färdig 1970 och användes i F-14 Tomcat jaktflygplan; och Texas Instruments TMS-0100-chip, tillkännagavs den 17 september 1971. MP944 var en samling av sex chips som bildade en enda processorenhet. TMS0100 -chipet presenterades som en "räknare på ett chip" med den ursprungliga beteckningen TMS1802NC. Detta chip innehåller en mycket primitiv CPU och kan bara användas för att implementera olika enkla fyrfunktionsräknare. Det är föregångaren till TMS1000 , som introducerades 1974, som anses vara den första mikrokontrollern - det vill säga en dator på ett chip som inte bara innehåller CPU, utan också ROM-, RAM- och I/O -funktioner. MCS-4-familjen med fyra chips utvecklade av Intel, varav 4004 är CPU eller mikroprocessor, var mycket mer mångsidig och kraftfull än TMS1000 med ett chip, vilket möjliggjorde skapandet av en mängd små datorer för olika applikationer.

Zilog , det första företaget helt tillägnat mikroprocessorer och mikrokontroller, startades av Federico Faggin och Ralph Ungermann i slutet av 1974.

Historia och produktion

Det första offentliga omnämnandet av 4004 var en annons i upplagan av Electronic News den 15 november 1971 . Den första leveransen var till Busicom för deras konstruktionsprototypkalkylator i mars 1971, följt av deras 141-PF-prototypkalkylator som var kommersiellt tillgänglig på marknaden i juli 1971. 4004 var förpackad i ett 16-stifts keramiskt dubbelradigt paket , den första kommersiellt tillgängliga datorprocessor konstruerad och tillverkad av chip tillverkaren Intel , som tidigare hade gjort halvledarminneskretsar. Chipets huvuddesigners var Federico Faggin , projektledare efter att den arkitektoniska definitionen slutfördes med Busicom, som skapade designmetoden och den kiselbaserade chipdesignen; Ted Hoff som formulerade arkitekturen, både av Intel, och Masatoshi Shima från Busicom som hjälpte till med utvecklingen.

Faggin, den enda chipdesignern bland ingenjörerna på MCS-4-projektet, var den enda med erfarenhet av slumpmässig logik och kretsdesign av metalloxidhalvledare (MOS) . Han hade också den avgörande kunskapen om den nya tekniken för kiselgrindprocess med självjusterade grindar , som han hade skapat på Fairchild 1968. På Fairchild 1968 konstruerade och tillverkade Faggin världens första kommersiella IC med SGT, Fairchild 3708 som fanns på omslaget till Electronics (29 september 1969). Så snart han gick med i Intel MOS -avdelningen skapade han en ny metod för slumpmässig logikdesign baserad på kiselgrind och bidrog med många teknik- och kretsdesignuppfinningar som gjorde det möjligt för deras single chip -mikroprocessor att bli verklighet. Hans metodik satte designstilen för alla tidiga Intel -mikroprocessorer och senare för Zilog Z80 . Han ledde också MCS-4-projektet och var ansvarig för det framgångsrika resultatet (1970–1971). Marcian "Ted" Hoff , chef för Application Research Department, bidrog med arkitektförslaget för Busicom i samarbete med Stanley Mazor 1969, sedan gick han vidare till andra projekt. På frågan om var han fick idéerna för arkitekturen för den första mikroprocessorn berättade Hoff att Plessey , "ett brittiskt traktorföretag", hade donerat en minidator till Stanford , och han hade "lekt med det lite" medan han var där. Shima utformade Busicom -kalkylatorns firmware och hjälpte Faggin under de första sex månaderna av implementeringen. Chefen för Intels MOS Designavdelning var Leslie L. Vadász . Vid utvecklingen av MCS-4 var Vadasz uppmärksamhet helt inriktad på den vanliga verksamheten för halvledarminnen och han överlämnade ledningen och ledningen av MCS-4-projektet till Faggin.

Busicom hade utformat sin egen special LSI chipset för användning i deras Busicom 141-PF räknare med integrerad skrivare. De baserade sin design på arkitekturen i Olivetti Programma 101 , en av världens första programmerbara räknare på bordsskivor , som Olivetti introducerade 1965. Busicom gav Intel i uppdrag att utveckla sin design för produktion. Precis som Olivetti Programma 101 använde Busicom-designen seriellt läs- och skrivminne. Busicom -minnet baserades på MOS -skiftregister snarare än det dyra Olivetti -minnet baserat på magnetostriktionstråd.

Intel bestämde att Busicom-designen var för komplex, eftersom serieminnen krävde fler komponenter och skulle använda 40 stift, en förpackningsstandard som skiljer sig från Intels egen 16-stifts standard. Intel föreslog att utveckla en ny design som skulle kunna produceras med standard 16-stifts DIP- förpackning, och skulle ha en reducerad instruktionsuppsättning. Minnesförenklingen kommer från att använda Intels nyutvecklade dynamiska RAM -minne. Denna nya design var 4004-chipet, som är en av en uppsättning av fyra chips, tillsammans med ROM , DRAM och serie-till-parallella skiftregisterchips. 4004 designades därefter av Federico Faggin med kiselgrindsteknik och byggdes av cirka 2 300 transistorer och följdes nästa år av den första 8-bitars mikroprocessorn, 3 500 transistorn 8008 (och 4040 , en reviderad och förbättrad 4004). Det var inte förrän utvecklingen av den 40-stiftiga 8080 1974, ett projekt tänkt och regisserat av Faggin som adress- och databussarna skulle separeras, vilket ger snabbare och enklare åtkomst till minne.

4004 använder en 10 μm process kisel-gate förbättring pMOS- teknik på en 12 mm 2 munstycke och kan utföra cirka 92 000 instruktioner per sekund ; en enda instruktionscykel är 10,8 mikrosekunder . Den ursprungliga klockfrekvensen design mål var ett MHz, samma som IBM 1620 Model I .

Intel 4004 designades genom att fysiskt skära Rubylith -ark i tunna remsor för att lägga ut kretsarna som ska skrivas ut, en process som föråldrades av nuvarande datorgrafikdesignmöjligheter.

För att testa de producerade chipsen utvecklade Faggin en testare för kiselskivor av MCS-4-familjen som själv drevs av 4004 chip. Testaren fungerade också som ett bevis för hanteringen att Intel 4004-mikroprocessorn inte bara kan användas i kalkylatorliknande produkter utan även för kontrollapplikationer.

Namn och varianter

När Faggin designade MCS-4-familjen, döpte han också chipsen med distinkta namn: 4001, 4002, 4003 och 4004, och bryt sig bort från numreringsschemat som Intel använde vid den tiden, vilket skulle ha krävt namnen 1302, 1105, 1507 respektive 1202. Hade han följt Intels nummersekvens hade tanken att chipsen var en del av en familj av komponenter avsedda att fungera sömlöst tillsammans gått förlorad. Intels tidiga numreringsschema för integrerade kretsar använde ett fyrsiffrigt nummer för varje komponent. Den första siffran indikerade den processteknologi som användes, den andra siffran angav den generiska funktionen och de två sista siffrorna i numret användes för att indikera det sekventiella numret i komponentens utveckling. 8008 -mikroprocessorn kallades ursprungligen 1201, enligt Intels namnkonventioner. Före dess introduktion på marknaden byttes 1201 till 8008, efter att den nya namnkonventionen startade med 4001/4002/4003/4004.

Tadashi Sasaki tillskriver den grundläggande uppfinningen att dela upp räknaren i fyra delar med ROM (4001), RAM (4002), skiftregister (4003) och CPU (4004) till en namnlös kvinna från Nara Women's College närvarande vid ett brainstormingmöte som var hölls i Japan innan hans första möte med Robert Noyce från Intel, som ledde fram till Busicom -affären.

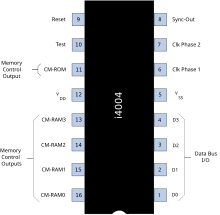

4004 är en del av MCS-4-familjen av LSI-chips som kan användas för att bygga digitala datorer med varierande mängder minne. De andra medlemmarna i MCS-4-familjen är minnen och ingångs-/utgångskretsar, som är nödvändiga för att implementera en komplett dator. 4001 är ett ROM (skrivskyddat minne) med fyra rader utgång; 4002 är ett RAM-minne (slumpmässigt åtkomstminne) med fyra rader ingång/utgång. 4003 är ett statiskt skiftregister som ska användas för att expandera I/O -linjerna; t.ex. för tangentbordsskanning eller kontroll av en skrivare.

4004 innehåller funktioner för direkt kontroll på låg nivå av val av minneschip och I/O, som normalt inte hanteras av mikroprocessorn; dess funktionalitet är dock begränsad genom att den inte kan exekvera kod från RAM -minnet och är begränsad till vilken instruktion som finns i ROM (eller ett oberoende laddat RAM -minne som fungerar som ROM - i båda fallen kan processorn själv inte skriva eller överföra data till en körbart minnesutrymme). RAM- och ROM-delarna var också ovanliga i integrationen av utgångsportar (och, i ROM-skivor, ingångar) som väsentligt reducerade minimideltalet i ett MCS-4-system, men som krävde inkludering av en viss processorliknande logik på chipsen själva för att acceptera, avkoda och köra dataöverföringsinstruktioner på relativt hög nivå.

Standardarrangemanget för ett 4004 -system är allt upp till 16 × 4001 ROM -chips (i en enda bank) och 16 × 4002 RAM -chips (i fyra banker om fyra), som tillsammans ger 4KB -programlagring, 1024 + 256 nibblar data /statuslagring, plus 64 utdata och 64 ingång/utmatning externa data/kontrolledningar (som själva kan användas för att driva, t.ex. en 4003). Intels MCS-4-dokumentation hävdar dock att upp till 48 ROM- och RAM-chips (med upp till 192 externa styrlinjer) "i valfri kombination" kan anslutas till 4004 "med enkel gating-hårdvara", men avböjer att ge ytterligare detaljer eller exempel på hur detta faktiskt skulle uppnås.

Tekniska specifikationer

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

- Maximal klockfrekvens är 740 kHz . 4004 hade denna maximala klockklassificering vid den första utgåvan 1971

- Instruktionscykeltid: minst 10,8 μs (8 klockcykler / maskincykel)

- Instruktionens körtid 1 eller 2 maskincykler (10,8 eller 21,6 μs), 46250 till 92500 instruktioner per sekund.

- Att lägga till två åttasiffriga tal (32 bitar vardera, förutsatt 4-bitars BCD-siffror) tar 850 μs, eller cirka 79 maskincykler (632 klockfickor), i genomsnitt på knappt 10 cykler (80 fästingar) per sifferpar och en hastighet på 1176 × 8-siffriga tillägg per sekund

- Separat program och datalagring. I motsats till Harvard-arkitekturdesigner , som använder separata bussar , använder 4004, med dess behov av att hålla ner stiftet, en enda multiplexerad 4-bitars buss för överföring:

- 12-bitars adresser

- 8-bitars instruktioner

- 4-bitars dataord

- Kan adressera 5120 bitar (motsvarande 640 byte) RAM, lagrat som 1280 4-bitars "tecken" och organiserade i grupper som representerar 1024 "data" och 256 "status" -tecken (512 och 128 byte).

- Kan direkt adressera 32 768 bitar ROM, motsvarande och ordnade som 4096 8-bitars ord (dvs byte).

- Instruktionssetet innehöll 46 instruktioner (varav 41 var 8 bitar breda och 5 var 16 bitar breda)

- Registeruppsättningen innehåller 16 register med 4 bitar vardera

- Intern subrutin stacken , 3 nivåer djup.

Logiska nivåer

| Symbol | Min | Max | Enhet |

|---|---|---|---|

| V SS - DD | +15-5% | +15+5% | V |

| V IL | V DD | V SS −5,5 | V |

| V IH | V SS −1,5 | V SS +0,3 | V |

| V OL | V SS −12 | V SS −6,5 | V |

| V OH | V SS −0,5 | V SS | V |

Stöd chips

- 4001: 256- byte ROM (256 8-bitars programinstruktioner ) och en inbyggd 4-bitars I/O- port. Ett 4001 ROM+I/O -chip kan inte användas i ett system tillsammans med ett 4008/4009 -par.

- 4002: 40-byte RAM (80 fyra-bit -data ord), och en inbyggd 4-bitars utgångsport; RAM-delen av chippet är organiserat i fyra "register" med 20 4-bitars ord:

- 16 dataord (används för mantissasiffror i den ursprungliga kalkylatordesignen), åtkomst på ett relativt standardiserat sätt, och

- 4 statusord (används för exponentsiffror och tecken i den ursprungliga kalkylatordesignen), åtkomliga med I/O -typkommandon istället för ROM: s ingångskanal

- 4003: 10-bitars parallell utgång skiftregister för avsökning tangentbord, displayer, skrivare etc.

- 4008: 8-bitars adresslås för åtkomst till vanliga minneschips och en inbyggd 4-bitars chip select och I/O-port

- 4009: program och I/O -åtkomstomvandlare till standardminne och I/O -chips

- 4269: tangentbord/skärmgränssnitt

- 4289: minnesgränssnitt (kombinerade funktioner 4008 och 4009)

Den lägsta systemspecifikation som beskrivs av Intel består av en 4004 med en enda 256-byte 4001 program-ROM; det finns inget uttryckligt behov av separat RAM i applikationer med minimal komplexitet tack vare 4004: s stora antal inbyggda indexregister, som motsvarar 16 × 4-bitars eller 8 × 8-bitars tecken (eller en blandning) av fungerande RAM, eller för enkla gränssnittschips tack vare ROM: s inbyggda I/O-linjer. Men när projektkomplexiteten ökar börjar de olika andra supportchipsna bli användbara.

Förpackning

Många versioner av Intel MCS-4-serien av processorer producerades. De tidigaste versionerna, märkta C (liksom C4004), var keramiska och använde ett zebramönster av vitt och grått på baksidan av chipsen, ofta kallade "gråspår". Nästa generation av chipsen var vanlig vit keramik (även märkt C) och sedan mörkgrå keramik (D). Många av de nyare versionerna av MCS-4-familjen tillverkades också med plast (P).

Använda sig av

Den första kommersiella produkten som använde en mikroprocessor var Busicom- kalkylatorn 141-PF. 4004 användes också i det första mikroprocessorstyrda flipperspelet , en prototyp som producerades av Dave Nutting Associates för Bally 1974.

Enligt Nick Tredennick , en mikroprocessordesigner och expertvittne till Boone/Hyatt -patentfallet:

Här är mina åsikter från [studien] [jag genomförde för patentfallet]. Den första mikroprocessorn i en kommersiell produkt var Four Phase Systems AL1 . Den första kommersiellt tillgängliga (säljs som en komponent) mikroprocessor var 4004 från Intel.

En populär myt säger att Pioneer 10 , det första rymdfarkosten som lämnade solsystemet, använde en Intel 4004 mikroprocessor. Enligt Dr Larry Lasher från Ames Research Center , utvärderade Pioneer -teamet 4004, men bestämde sig för att det var för nytt då för att inkludera i något av Pioneer -projekten. Myten upprepades av Federico Faggin själv i en föreläsning för Computer History Museum 2006.

Arv och värde

Federico Faggin undertecknade 4004 med sina initialer eftersom han visste att hans silikonportdesign förkroppsligade "mikroprocessorns väsen". I ett hörn av matrisen står det "FF"

Den 15 november 2006, 35 -årsjubileet för 4004, firade Intel genom att släppa chipets scheman , maskverk och användarmanual . En fullt fungerande 41 × 58 cm, 130 × skala kopia av Intel 4004 byggdes med diskreta transistorer och visades 2006 på Intel Museum i Santa Clara , Kalifornien.

Den 15 oktober 2010 tilldelades Faggin, Hoff och Mazor National Medal of Technology and Innovation av president Barack Obama för deras banbrytande arbete med 4004.

Se även

- Central Air Data Computer-den första 20-bitars militära mikroprocessorn släpptes i juni 1970 för US Navy F-14 Tomcat stridsflygplan, cirka 1,5 år innan Intel 4004 släpptes

Anteckningar

Referenser

Patent

- US 3753011 14 augusti 1973. Faggin, Federico: Inställbar bi-stabil krets för strömförsörjning.

- US 3821715 28 juni 1974. Hoff, Marcian; Mazor, Stanley; Faggin, Federico: Minnessystem för multi-chip digital dator.

Historiska dokument

- Faggin, Federico; Capocaccia, F. "A New Integrated MOS Shift Register", Proceedings XV International Electronics Scientific Congress, Rom, april 1968, s. 143–152. Det här dokumentet beskriver ett nytt statiskt MOS-skiftregister, utvecklat vid SGS-Fairchild (nu ST Micro) i slutet av 1967, innan Federico Faggin gick med i Fairchilds FoU i Palo Alto (Ca) i februari 1968. Faggin använde senare detta nya skiftregister i MCS-4-chipsen, inklusive 4004.

- Omslag och sammanfattning av IEDM -programmet (International Electron Devices Meeting) (oktober 1968) . Silicon Gate Technology (SGT) presenterades först av dess utvecklare, Federico Faggin, vid IEDM den 23 oktober 1968 i Washington, DC Det var den enda kommersiella processtekniken för tillverkning av MOS-integrerade kretsar med självjusterad grind som var senare universellt antagen av halvledarindustrin. SGT var den första tekniken för att producera kommersiella dynamiska RAM -minne, CCD -bildsensorer, icke -flyktiga minnen och mikroprocessorn, vilket för första gången gav alla grundläggande element i en dator för allmänna ändamål med LSI -integrerade kretsar.

- Omslag av Electronics Magazine (29 september 1969) . Elektronikartikeln introducerar Fairchild 3708, designad av Federico Faggin 1968. Det var världens första kommersiella integrerade krets med Silicon Gate -tekniken, vilket bevisar dess livskraft.

- Initialer FF (Federico Faggin) om 4004 -designen (1971) . 4004 bär initialerna FF av dess designer, Federico Faggin, etsade i ett hörn av chipet. Att signera chipet var en spontan gest av stolt författarskap och var också en originalidé som efterliknades av honom av många Intel -designers.

- Busicom 141-PF Printing Calculator Engineering Prototype (1971) . (Federico Faggins gåva till Computer History Museum, Mountain View, CA). CHM-samlingskatalogen visar bilder av den tekniska prototypen på Busicom 141-PF-datorräknaren. Den tekniska prototypen använde världens första mikroprocessor som någonsin har producerats. Denna unika prototyp var en personlig present av Busicoms president Yoshio Kojima till Federico Faggin för hans framgångsrika ledarskap för design och utveckling av 4004 och tre andra minne och I/O-chips (MCS-4-chipsetet ). Efter att ha förvarat det i sitt hem i 25 år donerade Faggin det till CHM 1996.

- Federico Faggin och ME Hoff: "Standarddelar och anpassad design smälter samman i processorsats med fyra chip". Elektronik/24 april 1972, s. 112–116. Omtryckt på s. 6–27 till 6–31 i Intel Memory Design Handbook: augusti 1973 .

- Federico Faggin, M. Shima, ME Hoff, Jr., H. Feeney, S. Mazor: "MCS-4 — An LSI micro computers system". IEEE '72 Region Six Conference. Omtryckt på s. 6–32 till 6–37 i Intel Memory Design Handbook: augusti 1973 .

Vidare läsning

- Federico Faggin, Marcian E. Hoff Jr., Stanley Mazor och Masatoshi Shima. 4004: s historia. IEEE Micro, 16 (6): 10-20, december 1996. "4004-designteamet berättar sin historia."

- Intel 4004 Microprocessor 35th Anniversary - Liveinspelning av presentationer av Ted Hoff och Federico Faggin vid Computer History Museum för 35 -årsjubileet för den första mikroprocessorn. ( youtube.com )

- IEEE Solid State Circuits Magazine, Winter 2009 Vol.1 No.1. "4004 mikroprocessorn av Faggin, Hoff, Mazor och Shima".

- MOS Silicon Gate Technology and the First Microprocessors , av Federico Faggin publicerad i La Rivista del Nuovo Cimento, Italian Physical Society, Vol. 38, nr 12, 2015.

- "Hur vi gjorde mikroprocessorn" av Federico Faggin. Nature Electronics, vol. 1, januari 2018. Publicerad online: 2018-01-08

externa länkar

- Intels första mikroprocessor - posten Intel 4004: Intel Museum (Intel Corporate Archives)

- Intel 4004: Ett vittnesmål från Federico Faggin, designer av 4004 och utvecklare av dess möjliggörande teknik

- Den nya metoden för slumpmässig logisk design som användes i 4004 och i alla tidiga Intel -mikroprocessorer

- Intervju med Masatoshi Shima

- MCS-4 Mikrodatoruppsättningsdatablad (12 sidor)

- Intel 4004 - 45th Anniversary Project , Schematics på den inofficiella 4004 -webbplatsen och en simulator i Java. Fullt funktionella 130x -repliker av 4004 byggda med diskreta transistorer.

- Den avgörande rollen för kiseldesign vid uppfinningen av mikroprocessorn

- Högupplösta ljusmikroskopbilder av en Intel 4004 dör tillsammans med en grundläggande förklaring av CMOS -logik

- Intel 4004 Emulator, Assembler och Disassembler: Enkla programmeringsverktyg för Intel 4004 i Javascript

- Datablad Intel 4004

- Datablad Intel MCS-4

- BuscomV2p1 schematisk

- MSC-4 monteringsspråk programmeringshandbok

- Chip Hall of Fame: Intel 4004 mikroprocessor ( IEEE Spectrum -webbplats)

- Berättelsen om Intel 4004